PROGRAMAÇÃO DO FPGA

1.

Introdução

Esse é um dos processos mais importante ao se trabalhar com um FPGA.

Durante a programação é que será definida a função lógica implementada

pelo FPGA.

A programação consiste em carregar o FPGA com os dados de programação

em linguagem binária. A maneira mais usada de se carregar esses bits de

configuração em um FPGA é serialmente, isto é, temos um bit de cada vez

sendo armazenado no FPGA.

Para que cada CLB e suas interconexões sejam configuradas são necessários

algumas centenas de bits.

Cada bit de configuração define o estado de uma célula de memória estática

(SRAM) que, ou controla um bit de uma função look-up table, ou seleciona uma

entrada de um multiplexador ou define o estado de um transistor em uma

interconexão.

Após configurado o chip pode ser testado. Uma característica

interessante em alguns tipos de FPGAs é que eles permitem uma reconfiguração

no próprio sistema onde se encontra. Isso agiliza o processo de teste e possíveis

reconfigurações. Esse tipo de programação será detalhada mais a frente.

2.

Ferramentas de desenvolvimento

Fazer a configuração de um

FPGA manualmente seria uma tafera simplesmente impensável devido a complexidade

do circuito. Por isso toda a parte de projeto, processamento, simulação e

programação do FPGA é normalmente feita através de programas específicos.

Cada fabricante disponibiliza programas que suportam seus próprios FPGAs

ou fazem parcerias com empresas que produzam tais programas.

O programa que a ALTERA utiliza para fazer a programação de suas PLDs

se chama MAX+PLUS II, a XILINX disponibiliza o programa FOUNDATION.

O MAX+PLUS é capaz de receber as descrições do circuito, em linguagem

VHDL por exemplo, provenientes de outros programas ou criado no próprio MAX+PLUS,

e gerar arquivos de programação que serão utilizados na configuração da

PLD.

Para se programar o chip

é necessário então transformar a informação desses arquivos de configuração

para uma linguagem binária e carregar esses bits para as memórias estáticas

do chip. O próprio MAX+PLUS pode fazer esse trabalho, porém é possível

utilizar programas de outras empresas que suportem os chips da ALTERA para fazer

a transformação e o armazenamento dos dados de configuração no chip.

O FPGA pode ser

carregado com os dados de programação através da porta paralela ou serial de

um computador ou através de uma PROM que já contenha todos os bits que serão

utilizados para a configuração do chip. No primeiro caso é possível

controlar a programação do chip pelo computador, enquanto que no segundo caso

após carregada as informações na PROM não necessitamos mais de um computador

controlando a entrada de dados no chip, teremos um circuito adcional fazendo

esse controle.

3.

Programação em Sistema (ISP)

3.1.

Conceito

Programação em sistema

consiste basicamente numa tecnologia que permite a configuração, reconfiguração

e testes do FPGA sem ter que retirá-lo do circuito onde se encontra. Utilizando

a porta serial ou paralela de um computador para se conectar a um FPGA é possível,

utilizando programas específicos, programar o FPGA, verificar sua programação,

testá-lo com determinadas entradas e comparar suas saídas com as saídas

esperadas, etc.

3.2.

Vantagens em relação a outros tipos de PLDs

PLDs que se utilizam da

tecnologia ISP possuem várias vantagens em relação a PLDs que não possuem

essa tecnologia. Citaremos algumas dessas vantagens.

Não é necessário o

uso de soquete. Já que a PLD pode ser reconfigurada enquanto está no circuito

ela pode ser logo soldada na placa. Essa facilidade de reconfiguração permite

ao projetista fazer alterações mais rápidas no dispostivo, o que reduz o

tempo de programação, e diminui a probabilidade de acontecer algum dano devido

ao excesso de manuseio.

Outra vantagem é que o layout da placa pode ser feito durante a própria

fase de projeto da lógica diminuindo ainda mais o tempo de fabricação de uma

placa.

3.3.

Ferramentas usadas para implementar a ISP

Existem vários tipos de

softwares e hardwares que podem ser utilizados para se implementar a programação

em sistema. Falaremos apenas de um tipo de software e um de hardware. Apesar de

falarmos de apenas um número reduzido de ferramentas, é mais do que suficiente

para retratar o processo de programação em sistema.

3.3.1.

Linguagem JAM

Jam é uma linguagem otimizada

para a programação de PLDs através de uma interface chamada JTAG, que será

descrita mais a frente. A sintaxe dessa linguagem é bem parecida com BASIC, com

instruções e aspectos adicionais ligados diretamente a interface JTAG. Abaixo

temos o fluxo básico da linguagem JAM.

Figura – Fluxo Básico

da Linguagem JAM

O JAM Composer é um programa

criado por algum fabricante de PLDs que gera um arquivo JAM para programar uma

de suas PLDs. Temos como exemplo o MAX+PLUS II.

O arquivo JAM contém tanto os dados de programação quanto o algoritmo

de programação necessário para programar a PLD.

O JAM Player é um

programa que interpreta o arquivo JAM e através da interface JTAG programa a

PLD.

Qualquer JAM Player pode ler um arquivo JAM criado por um JAM Composer de

qualquer fabricante, o que garante uma independência de fabricante.

Um arquivo JAM, apesar de ser do tipo ASCII e conter tanto os dados de

programação quanto o algoritmo de programação, é muito compacto, o que

proporciona maior rapidez no processamento. Um método utilizado para se atingir

essa nível de compactação foi o de comprimir os dados de programação.

3.3.2.

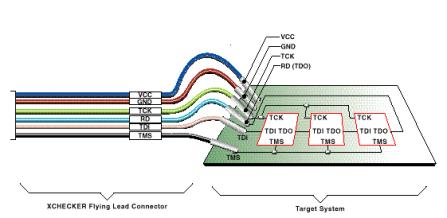

Interface JTAG

JTAG é um

tipo de interface de testes e programação padronizada que serve para

interligar uma porta paralela ou serial com uma PLD .

Essa interface

conecta-se normalmente com o chip através de 4 pinos sendo possível usar até

5 pinos em alguns casos. A PLD pode então ser programada através dessa

interface, comandada por um programa, como o JAM Player, descrito acima.

Figura – Ligação Serial – PLD via interface JTAG

[Índice]