1.

Introdução

São

dispositivos lógico-programáveis que possuem mais de 600 portas. Quanto maior

o número de portas do PLD, maior será

sua complexidade, principalmente no que se refere a estuturas de conexão.

Os HCPLD são divididos, basicamente , em CPLD (Complex Programable Logic Devices) e FPGA (Field Programable Gate Array). Sua diferença básica reside no método

de interligação das células.}

2. Estruturas Básicas

Um

CPLD é constituído por várias estruturas repetidas conhecidas como células. Em cada célula temos elementos que implementam lógica

combinacional acompanhados de Lachtes

(através de Memórias e Flip-Flops) destinados a aplicações de lógica

sequencial. Interligando estas duas estruturas, temos multiplexadores programáveis

que realizam a interligação destes blocos entre si

e destes com o exterior da célula (para outra célula ou para

barramentos).

Um barramento é uma estrutura que se destina a promover a interligação

entre as células. São conexões físicas (trilhas metalizadas) disponíveis no

interior do chip. Dependendo do tipo

de PLD envolvido (FPGA ou CPLD), de sua complexidade e de seu fabricante, temos

diferentes recursos e modos de conexão. Basicamente temos estruturas de conexão

segmentadas (FPGA) e estruturas contínuas

(CPLD).

Para interface com o mundo

exterior temos unidades conhecidas como blocos

de entrada e saída. Sua função é conectar as células aos pinos do

integrado que normalmente pode ser realizada diretamente (Célula ®

Bloco I/O) ou indiretamente (Célula ®

Barramento ®Bloco

I/O) .

2.1 Célula

Lógica

2.1.1

Introdução

Vamos entender por célula todo

conjunto ou bloco lógico que possui conexão com os barramentos do integrado.

Tal ênfase se faz necessária pois observamos variações significativas entre

os vários tipos de HCPLD e entre seus diversos fabricantes (mencionadas

posteriormente).

2.1.2.

Elementos Geradores de Lógica Combinacional

No interior de cada célula, percebemos dois tipos possíveis de

implementações de lógica combinacional: a matriz de Ors

e Ands e o Look-Up Table.

Observamos que na medida que cresce a complexidade do PLD, a última estrutura é preferida, inclusive pela sua dupla

funcionalidade (Memória x Gerador de Função Lógica).

2.1.2.1

Matriz Programável de ANDs e ORs

É uma estrutura utilizada em PLDs

mais simples, desde dos PALs. Esta

matriz implementa uma função lógica através da soma de produtos (representação

em Mintermos). Através do processo de configuração ou programação,

ativam-se chaves lógicas que interconectam entradas as portas AND, definindo-se

quais variáveis farão parte do Mintermo em questão. Posteriormente,

configuram-se quais Mintermos que entrarão na porta

OR, realizando assim a soma dos mintermos desejados.

Em certas implementações, pode ser necessário que o resultado de um

Mintermo seja colocado na entrada de um outro Mintermo. Para tal caso, existem

estruturas que permitem realimentações ou seja que a saída de uma AND seja

redirecionada para a matriz de configuração, podendo ser direcionada para uma

outra AND qualquer.

Existem PLDs em que buscam contornar as limitações do número de ANDs

e Ors e de suas interconexões possíveis (com elementos do

interior e do exterior da célula) implementando estruturas

complemen-tares tais como Expansores de Lógica Paralela e Expansores Lógicos

para Partilha de Dados.

Em funções mais complexas, pode ser necessário o cascateamento de mintermos. Assim, temos vários níveis lógicos envolvidos e um maior atraso na produção da saída, assim como eventuais problemas de glitch.

Em

resumo, esta estrutura possui a função única de gerar uma função lógica

das entradas e sua programação em

certos casos pode se tornar complexa.

2.1.2.2.

Look-Up Table (LUT)

O LUT é basicamente uma memória

pre-programada que fornece uma saída dado um conjunto de variáveis de entrada.

Assim, enquanto a matriz de AND e OR produz para cada entrada um valor de saída,

o LUT não realiza operação lógica

nenhuma, ele apenas consulta a tabela verdade da função que nele foi

programada.

Mas o que é uma memória?

Como utilizar uma memória para implemetar um LUT?

Na figura acima temos o diagrama funcional de uma memória de 16 posições

de 1 bit. Tal memória pode ser utilizada portanto como um LUT de 4 bits pois 24

= 16 , ou seja, 16 são as linhas da tabela verdade de qualquer função de 4

variáveis.

Uma memória é um conjunto de Latches

selecionáveis. No caso anterior temos 16 Latches

que podem ser selecionados para leitura, via o endereço de leitura, e para

escrita, via endereço de escrita.

Para

programação, deve-se colocar as variáveis de entrada da função no endereço

de escrita e o valor correspondente a saída desejada em DIN. Para

leitura, devemos colocar as mesmas variáveis no endereço de leitura e o valor

da função deve ser tomada em G.

Percebemos que para uso como LUT, o bloco de memória deve ser

configurado apenas para leitura. Como o LUT não realiza combinação lógica

das variáveis de entrada, não há níveis lógicos, logo o atraso da função

lógica é dependente apenas do tempo de leitura da memória que o implementa.

Esta estrutura é preferida pelos fabricantes, sobretudo nos PLDs

mais complexos. Soma-se ao fator anterior a facilidade de programação,

versatilidade e dupla funcionalidade: uma mesma estrutura pode implementar tanto

um LUT quanto um Registrador ou Latch.

Observamos que uma memória de 16 posições de 4 bits pode implementar 4

funções lógicas diferentes de 4 variáveis. Certos fabricantes

disponibilizam, em certas arquiteturas, um bloco de bloco de memória pode ser

configurado com diferentes tipos de acesso e tamanho de dados. (Vide Figura)

2.1.3.

Estruturas Interna das Células

2.1.3.1.

CPLD

Observamos nos CPLDs mais complexos que cada célula lógica, também conhecida

como Logic Array Block (LAB), é

constituída por unidades básicas conhecidas com Logic

Elements (LE). Os Logic Elements por sua vez possuem LUTs, Flip-Flops (implementam registradores) e lógicas para

interconexão entre Logic Elements

adjacentes (Carry Chain e Cascade Chain).

A Carry Chain é destinada a

geração a propagação de Carry rápida. Ela permite implementar funções combinacionais das

entradas com a Carry do LE anterior.

Um aplicação interessante é a implementação de somadores de n bits. Como

cada LAB possui 10 LE e um deles é utilizado para controle, podemos implementar

um somador de 9 bits com apenas uma célula.

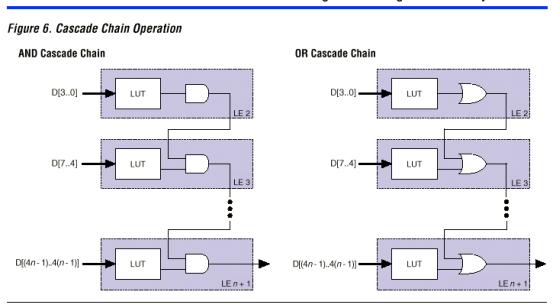

A Cascade Chain consiste em

portas OR ou AND que podem combinar dados provenientes de LUTs

de diferentes LE. Assim, podem ser gerados a combinação de mintermos (AND) ou

maxtermos (OR) pelo cascateamento das saídas dos diferentes LE via portas AND

ou OR.

Observamos ainda dois multiplexadores programáveis destinados a utlização

do LE; um deles para fazer Register Bypass,

ou seja, chavear a utilização do LE entre dois modos: lógica combinacional ou

lógica sequencial e o outro para definições do bloco de memória (lógica

sequencial).

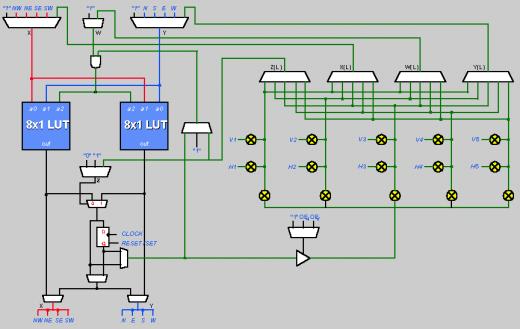

2.1.3.2.

FPGA

Neste tipo de arquitetura, presenciamos em cada célula 2 LUTs,

um Flip-Flop e vários multiplexadores

destinados a seleção do modo de operação (lógica combinacional ou lógica

sequencial) assim como definição das ligações da célula com os barramentos

(V1 a V5 e H1 a H5) e da célula com outras células adjacentes nas direções:

N,S,L,O (ortogonais a célula) e NW, NE, SW, SE (diagonais a célula).

Verificamos também que podem ser definidas a conexão entre os barramentos no

interior da célula.

2.2.

Blocos de Entrada e Saída

Os blocos de entrada e saída conectam a lógica implementada no interior

do PLD ao mundo externo. De maneira bastante simplificada, podemos dizer que

eles se consistem de dois TRI-STATES: um que opera na entrada de dados (mundo

externo ®

integrado) e outro que opera na saída. Como ambos TRI-STATES são programáveis,

podemos definir um pino de conexão do CI como entrada, saída ou ambas

(comunicação bidirecional).

A fim de permitir o interfaceamento com componentes de diferentes

tecnologias e diferentes velocidades e lógicas (positiva e negativa), existem

blocos internos destinados ao controle de Delay,

Slew Rate, nível de tensão e polaridade dos sinais de entrada e saída.

Complementar a isto, temos a lógica de PULL-UP ou PULL-DOWN, onde se

pode definir uma entrada a priori (alto ou baixo), minimizando o número de

conexões externas do integrado.

2.3.

Estruturas de Interconexão

Para conexão entre as células e entre as células e os blocos de saída,

os HCPLDs possuem estruturas conhecidas como barramentos. Para os CPLDs mais

complexos e para os FPGA, verificam-se barramentos horizontais e verticais

adjacentes a cada célula.

Uma primeira diferença entre os CPLDs e os FPGAs está na granularidade

de suas células. Um FPGA é mais granular que um CPLD pois, conforme vimos, em

um CPLDs temos dez LE conectáveis entre si em cada célula enquanto que em um

FPGA possui equivalentemente um LE por célula.

Devido a esta maior granularidade verificamos que em um FPGA existe um

forte dependência do roteamento o que pode ser inclusive percebido pelo elevado

número de mulplexadores por célula. Em um FPGA a definição das variáveis de

entrada é feita internamente (célula lógica) enquanto que em um CPLD, esta é

feita externamente.

· FPGA (Disposição das Células)

· FPGA (Conexões Célula x Barramentos)

· CPLD (Disposição das Células e Barramentos)

3.

Comparação e Características das Estruturas

A diferença fundamental entre um CPLD e um FPGA está na estrutura de

constituição dos barramentos. Um CPLD é constituído por barramentos contínuos

enquanto que um FPGA, por barramentos segmentados.

Um barramento contínuo é constituído por linhas de metal de

comprimento uniforme que atravessam o integrado no comprimento e na largura

(vertical x horizontal). Assim, a resistência e a capacitância de todas

interconexões é fixa, fazendo com que os intervalos de propagação (delay)

entre quaisquer duas células lógicas do dispositivo seja constante.

Um barramento segmentado é constituído por vários segmentos de metal

que também atravessam o integrado nas direções horizontal e vertical. Estes

segmentos podem ser conectados de diversas maneiras através de chaves lógicas

programáveis existentes entre eles. Assim, o número de segmentos requeridos

para conexão entre duas células não é constante ou previsível, depende

fortemente da disposição da células e das

múltiplas possibilidades de interconexão entre elas. Como não sabemos,

antes do roteamento (interconexão das células), o número de segmentos

requeridos para conexão entre células, não podemos quantizar os atrasos de

propagação. O atraso de uma dada estrutura lógica é função de um atraso

devido ao barramento que varia de caso a caso mais o atraso da estrutura.

A menor granularidade do CPLD, juntamente com sua estrutura de conexão

contínua, facilita sua programação, possibilita melhor perfor-mance do

sistema (Propagation Delay fixo) e

permite melhor utilização das células lógicas para certas aplicações. A

estrutura contínua permite ainda que pequenas modificações na lógica sejam

feitas sem degradação na performace. Como um FPGA depende fortemente do

roteamento, estas mesmas modificações poderiam acaretar numa queda sensíveis

de performace devido a necessidade de um novo roteamento.

Por outro lado, a granularidade do FPGA dá uma grande flexibilidade e pode ser desejável em certa aplicações.

Concluímos que a escolha de um ou outro é função direta das necessidades de um projeto. Cabe ao projetista escolher a tecnologia e o dispositivo mais adequado a implementação em questão.

[Índice]