APLICAÇÕES

DE FPGA’s

FPGAs podem ser

utilizados na implementação de uma grande quantidade de funções lógicas,

havendo uma certa limitação para o número de variáveis de entrada , como é

o caso dos outros dispositivos existentes no mercado.

As implementações consistem desde simples circuitos, como somadores,

subtratores e acumuladores, até circuitos mais complexos, como filtros e DSPs.

Dentre as aplicações

mais simples, podemos também citar codificadores (como exemplo o codificador

entre bcd e binário), decodificadores e somadores com carry look-ahead.

Existem várias maneiras de se implementar somadores binários,

subtratores e acumuladores em FPGA. Vários métodos oferecem diferentes

características entre velocidade e tamanho.

Uma técnica mais compacta, mas lenta, é a técnica bit-serial, que

opera em um ou dois bits por ciclo de clock, gerando soma e carry. A soma é

alimentada para um registrador de saída e o carry é armazenado e usado no próximo

bit.

O mais compacto circuito combinacional somador ou subtrator (paralelo), consiste de cascatas de CLBs. Cada CLB implementa

um somador completo, recebendo um bit de cada operando e um carry de entrada. o

CLB gera a soma e um carry de saída. Uma função de 16 bits é complementada

com 16 CLBs de atraso, e requer 16 CLBs.

Para FPGAs que possuem

geradores de funções com 5 entradas a adição pode ser feita de dois em dois

bits. Cada conjunto de 3 CLBs pode operar dois bits de entrada de cada um dos

operandos e um carry de entrada, gerando um carry de saída e os dois bits de saída

da soma. Uma função de 16 bits requer 24 CLBs mas o operação é feita em 8

atrasos de CLB.

Para uma operação mais rápida pode ser implementado o carry look-ahead

que usa propagador de carry e gerador de carry para reduzir o tempo de atraso.

Usando esta técnica, uma adição de 16 bits pode ser feita em 5 atrasos de CLB,

usando 30 CLBs.

A forma mais rápida de implementar uma soma foi inventada por J.

Sklansky e chamada de Algorítimo de Soma Condicional, e implementa uma soma de

16 bits com apenas 3 atrasos de CLB, usando 41 CLBs.

1. EXEMPLO: SOMADOR BIT-SERIAL

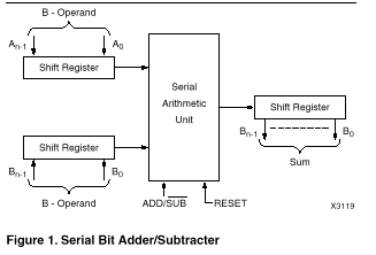

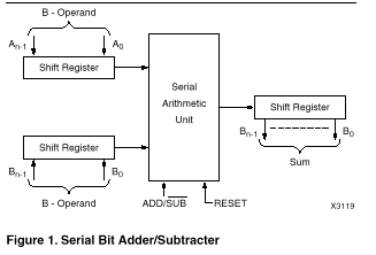

A arquitetura do CLB é ideal para implementação do circuito aritmético

bit-serial. Os dois operandos são serialmente registrados nos shift registers e

enviados em LSB (bit menos siginificativo) para a unidade aritmética serial. A

soma é também gerada serialmente e convertida para dados paralelos num

terceiro registrador.

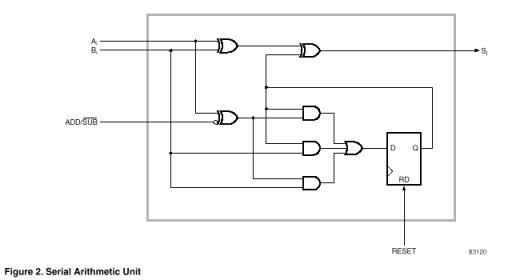

A unidade aritmética

possui um somador/subtrator completo de 1-bit e um carry/borrow flip-flop, e

pode ser implementada num único CLB. Antes de iniciar a operação, o carry/borrow

flip-flop precisa ser apagado. Subsequentemente, somas ou diferenças são

passadas para o registrador de saída, enquanto carries e borrows são

armazenados para inclusão no próximo bit da operação serial.

[Índice]