PCI

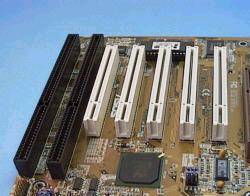

Forma do barramento:

![]()

O barramento PCI ( Peripheral Component Interconnect ) foi criado

originalmente durante o desenvolvimento do microprocessador Pentium, pela INTEL

em conjunto com outros fabricantes, porém, algumas Placas 486 também possuem o

slot PCI.

Atualmente esse tipo de barramento é usado por diferentes

processadores.

Este barramento possui duas versões, que estão abaixo

mostradas:

Versão

1.0

·

Baseado no projeto

"VESA Local Bus",conhecido como VLB, era considerada um tipo de

barramento local e não barramento principal, tais como: ISA, EISA(Este

barramento foi feito especificamente de modo que placas para barramento ISA

possam nele ser plugados, bem como novas placas com capacidade para 32 bits de

dado) e MCA(sistemas PS/2 de topo de linha da IBM).

·

Utilizado a 33 MHz;

·

Possui largura de 32 bits

em uma conexão de 124 pinos;

·

Desempenho calculado

= 32 (bits) x 33 (MHz) / 8 (bits) = 132 Mbits/s;

·

Suporta muitos

dispositivos

Versão

2.0

·

Projetado para ser

independente do microprocessador;

·

Sincronizado com o

Clock do microprocessador de 20 a 33 MHz;

·

Possui largura de 64

bits em uma conexão de 188 pinos;

·

Desempenho calculado

= 64 (bits) x 33 (MHz) / 8 (bits) = 264 Mbits/s;

Os slots PCI de 64 bits são um pouco maiores que os de 32,

sendo que nas placas atuais o segundo tipo é mais utilizado.

As placas de expansão PCI possuem um recurso muito interessante, além da sua elevada velocidade de transferência de dados. Trata-se da autoconfiguração obtida com o padrão PnP (Plug and Play). Essas placas são reconhecidas e configuradas automaticamente pelo BIOS (todas as placas de CPU equipadas com slots PCI possuem um BIOS PnP) e pelo sistema operacional sem necessitarem que o usuário precise posicionar jumpers para realizar manualmente a sua configuração, como ocorria com as placas de expansão até pouco tempo atrás.

Essa autoconfiguração ocorre pois

existe uma EEPROM especial que contém informações sobre o endereço e a

interrupção(IRQ).

Dispositivos PCI são projetados para permitir o compartilhamento

de uma mesma IRQ pois as manipulam de forma diferente. Se for necessário usar

uma interrupção normal, o chipset (ou BIOS) mapeará a interrupção para uma

interrupção normal do sistema (normalmente usando alguma interrupção entre a

IRQ 9 e IRQ 12).

A velocidade do clock do barramento pode depender da

velocidade dos clock interno do microprocessador, e como já foi dito, essa freqüência em geral é de 33 MHz, mas dependendo do

processador, pode ter um clock de 30 ou 25 MHz. A tabela que segue mostra a

relação entre o clock do barramento PCI e o clock interno do processador.

·

Clock externo

e interno do microprocessador,

o clock externo é sempre igual a uma fração do clock interno. Esta fração pode

ser 2/3, 1/2, 2/5, ou 1/3 dependendo do valor do clock interno. Estas divisão é

feita pelo microprocessador.

·

Clock do

barramento PCI, o clock do

barramento PCI é sempre igual à metade do clock externo do microprocessador que

é feita por um VLSI(chip responsável pela integração dos componentes) que

controla o acesso ao barramento PCI.

|

Clock Interno |

Fração |

Clock

Externo |

Clock

PCI |

|

75

MHz |

2/3 |

50

MHz |

25

MHz |

|

100

MHz |

2/3 |

66

MHz |

33

MHz |

|

133

MHz |

1/2 |

66

MHz |

33

MHz |

|

150

MHz |

2/5 |

60

MHz |

30

MHz |

|

166

MHz |

2/5 |

66

MHz |

33

MHz |

|

200

MHz |

1/3 |

66

MHz |

33

MHz |

·

O barramento PCI pode

ser usado pelos slots PCI, e pelas interfaces IDE e USB.

O barramento PCI é o barramento

mais utilizado atualmente, já que ele é muito mais rápido que os barramentos ISA,

tem como vantagem o fato de trabalhar independentemente do processador (

trabalhar paralelamente a ele), além de possuir uma grande compatibilidade, uma

vez que ele não funciona para computadores com processador Pentium,

diferentemente dos barramentos intermediários entre ele e o ISA.

Inclusive, nas placas atuais o barramento ISA é acessado

através do barramento PCI. Agora serão relacionadas as características

principais deste barramento :

·

Bus mastering

- O periférico pode controlar o barramento e acessar memória sem a

interferência do processador, como em DMA.

·

Plug-And-Play (previamente explicado)

·

Modelos

·

32 bits a 33MHz (mais

utilizados - taxa de transferência de 132 MBytes/s)

·

64 bits a 66MHz (264

Mbytes/s)

·

32 bits a 33MHz (264

Mbytes/s)

·

64 bits a 66MHz (528

Mbytes/s)

·

Slots de 5V (mais

comuns) e 3,3 V (66MHz utiliza sempre esta tensão). Existem placas específicas

ou universais.

A ligação do barramento local com o barramento PCI chama-se host-PCI bridge. Já a ligação entre o

barramento PCI com o ISA chama-se PCI-ISA

bridge. Também são conhecidas como ponte norte e ponte sul.

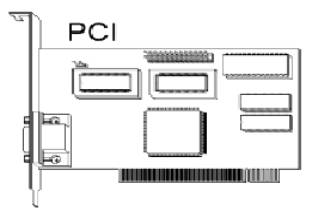

Outra vantagem ocorre em relação ao

tamanho da placa, uma vez que ela se torna menor do que uma placa ISA, desta

maneira ocupando um espaço menor dentro do gabinete, o que resulta em uma

melhor circulação de ar no interior dele, possibilitando que o processador

tenha um menor aquecimento, não só prolongando desta maneira sua vida útil,

como também possibilitando uma redução na energia consumida pelo

microcomputador.

Até pouco tempo, a maioria dos PCs equipados com

processadores Pentium e superiores utilizavam placas de vídeo PCI. Depois da

criação do barramento AGP, placas de vídeo AGP têm se tornado cada vez mais

comuns, sendo que as vantagens deste tipo de barramento serão explicadas

adiante.

Além das placas PCI

para vídeo(caso de placas VGA e SVGA), podemos utilizar esse barramento possui

outros tipos de placa, como por exemplo:

·

Placa de rede PCI

·

Digitalizadoras de

vídeo PCI

·

Controladoras SCSI

PCI

·

Placas de som PCI

·

Placas de modem PCI

Exemplo: Placa de video

Pinagem do Pci:

PCI Universal Card 32/64 bit

----------------------------------------------------------------

| PCI Component Side (side B) |

| |

| |

| optional |

| ____ mandatory 32-bit pins 64-bit pins _____|

|___| |||||||--|||||||||||||||||--|||||||--||||||||||||||

^ ^ ^ ^ ^ ^ ^ ^

b01 b11 b14 b49 b52 b62 b63 b94

PCI 5V Card 32/64 bit

| optional |

| ____ mandatory 32-bit pins 64-bit pins _____|

|___| ||||||||||||||||||||||||||--|||||||--||||||||||||||

PCI 3.3V Card 32/64 bit

| optional |

| ____ mandatory 32-bit pins 64-bit pins _____|

|___| |||||||--||||||||||||||||||||||||||--||||||||||||||

Características dos

pinos:

98+22 PIN EDGE CONNECTOR at the computer.

|

Pin |

+5V |

+3.3V |

Universal |

Description |

|

A1 |

TRST |

|

|

Test Logic Reset |

|

A2 |

+12V |

|

|

+12 VDC |

|

A3 |

TMS |

|

|

Test Mde Select |

|

A4 |

TDI |

|

|

Test Data Input |

|

A5 |

+5V |

|

|

+5 VDC |

|

A6 |

INTA |

|

|

Interrupt A |

|

A7 |

INTC |

|

|

Interrupt C |

|

A8 |

+5V |

|

|

+5 VDC |

|

A9 |

RESV01 |

|

|

Reserved VDC |

|

A10 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A11 |

RESV03 |

|

|

Reserved VDC |

|

A12 |

GND03 |

(OPEN) |

(OPEN) |

Ground or Open (Key) |

|

A13 |

GND05 |

(OPEN) |

(OPEN) |

Ground or Open (Key) |

|

A14 |

RESV05 |

|

|

Reserved VDC |

|

A15 |

RESET |

|

|

Reset |

|

A16 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A17 |

GNT |

|

|

Grant PCI use |

|

A18 |

GND08 |

|

|

Ground |

|

A19 |

RESV06 |

|

|

Reserved VDC |

|

A20 |

AD30 |

|

|

Address/Data 30 |

|

A21 |

+3.3V01 |

|

|

+3.3 VDC |

|

A22 |

AD28 |

|

|

Address/Data 28 |

|

A23 |

AD26 |

|

|

Address/Data 26 |

|

A24 |

GND10 |

|

|

Ground |

|

A25 |

AD24 |

|

|

Address/Data 24 |

|

A26 |

IDSEL |

|

|

Initialization Device Select |

|

A27 |

+3.3V03 |

|

|

+3.3 VDC |

|

A28 |

AD22 |

|

|

Address/Data 22 |

|

A29 |

AD20 |

|

|

Address/Data 20 |

|

A30 |

GND12 |

|

|

Ground |

|

A31 |

AD18 |

|

|

Address/Data 18 |

|

A32 |

AD16 |

|

|

Address/Data 16 |

|

A33 |

+3.3V05 |

|

|

+3.3 VDC |

|

A34 |

FRAME |

|

|

Address or Data phase |

|

A35 |

GND14 |

|

|

Ground |

|

A36 |

TRDY |

|

|

Target Ready |

|

A37 |

GND15 |

|

|

Ground |

|

A38 |

STOP |

|

|

Stop Transfer Cycle |

|

A39 |

+3.3V07 |

|

|

+3.3 VDC |

|

A40 |

SDONE |

|

|

Snoop Done |

|

A41 |

SBO |

|

|

Snoop Backoff |

|

A42 |

GND17 |

|

|

Ground |

|

A43 |

PAR |

|

|

Parity |

|

A44 |

AD15 |

|

|

Address/Data 15 |

|

A45 |

+3.3V10 |

|

|

+3.3 VDC |

|

A46 |

AD13 |

|

|

Address/Data 13 |

|

A47 |

AD11 |

|

|

Address/Data 11 |

|

A48 |

GND19 |

|

|

Ground |

|

A49 |

AD9 |

|

|

Address/Data 9 |

|

A52 |

C/BE0 |

|

|

Command, Byte Enable 0 |

|

A53 |

+3.3V11 |

|

|

+3.3 VDC |

|

A54 |

AD6 |

|

|

Address/Data 6 |

|

A55 |

AD4 |

|

|

Address/Data 4 |

|

A56 |

GND21 |

|

|

Ground |

|

A57 |

AD2 |

|

|

Address/Data 2 |

|

A58 |

AD0 |

|

|

Address/Data 0 |

|

A59 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A60 |

REQ64 |

|

|

Request 64 bit ??? |

|

A61 |

VCC11 |

|

|

+5 VDC |

|

A62 |

VCC13 |

|

|

+5 VDC |

|

|

|

|

|

|

|

A63 |

GND |

|

|

Ground |

|

A64 |

C/BE[7]# |

|

|

Command, Byte Enable 7 |

|

A65 |

C/BE[5]# |

|

|

Command, Byte Enable 5 |

|

A66 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A67 |

PAR64 |

|

|

Parity 64 ??? |

|

A68 |

AD62 |

|

|

Address/Data 62 |

|

A69 |

GND |

|

|

Ground |

|

A70 |

AD60 |

|

|

Address/Data 60 |

|

A71 |

AD58 |

|

|

Address/Data 58 |

|

A72 |

GND |

|

|

Ground |

|

A73 |

AD56 |

|

|

Address/Data 56 |

|

A74 |

AD54 |

|

|

Address/Data 54 |

|

A75 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A76 |

AD52 |

|

|

Address/Data 52 |

|

A77 |

AD50 |

|

|

Address/Data 50 |

|

A78 |

GND |

|

|

Ground |

|

A79 |

AD48 |

|

|

Address/Data 48 |

|

A80 |

AD46 |

|

|

Address/Data 46 |

|

A81 |

GND |

|

|

Ground |

|

A82 |

AD44 |

|

|

Address/Data 44 |

|

A83 |

AD42 |

|

|

Address/Data 42 |

|

A84 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

A85 |

AD40 |

|

|

Address/Data 40 |

|

A86 |

AD38 |

|

|

Address/Data 38 |

|

A87 |

GND |

|

|

Ground |

|

A88 |

AD36 |

|

|

Address/Data 36 |

|

A89 |

AD34 |

|

|

Address/Data 34 |

|

A90 |

GND |

|

|

Ground |

|

A91 |

AD32 |

|

|

Address/Data 32 |

|

A92 |

RES |

|

|

Reserved |

|

A93 |

GND |

|

|

Ground |

|

A94 |

RES |

|

|

Reserved |

|

|

|

|

|

|

|

B1 |

-12V |

|

|

-12 VDC |

|

B2 |

TCK |

|

|

Test Clock |

|

B3 |

GND |

|

|

Ground |

|

B4 |

TDO |

|

|

Test Data Output |

|

B5 |

+5V |

|

|

+5 VDC |

|

B6 |

+5V |

|

|

+5 VDC |

|

B7 |

INTB |

|

|

Interrupt B |

|

B8 |

INTD |

|

|

Interrupt D |

|

B9 |

PRSNT1 |

|

|

Reserved |

|

B10 |

RES |

|

|

+V I/O (+5 V or +3.3 V) |

|

B11 |

PRSNT2 |

|

|

?? |

|

B12 |

GND |

(OPEN) |

(OPEN) |

Ground or Open (Key) |

|

B13 |

GND |

(OPEN) |

(OPEN) |

Ground or Open (Key) |

|

B14 |

RES |

|

|

Reserved VDC |

|

B15 |

GND |

|

|

Reset |

|

B16 |

CLK |

|

|

Clock |

|

B17 |

GND |

|

|

Ground |

|

B18 |

REQ |

|

|

Request |

|

B19 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

B20 |

AD31 |

|

|

Address/Data 31 |

|

B21 |

AD29 |

|

|

Address/Data 29 |

|

B22 |

GND |

|

|

Ground |

|

B23 |

AD27 |

|

|

Address/Data 27 |

|

B24 |

AD25 |

|

|

Address/Data 25 |

|

B25 |

+3.3V |

|

|

+3.3VDC |

|

B26 |

C/BE3 |

|

|

Command, Byte Enable 3 |

|

B27 |

AD23 |

|

|

Address/Data 23 |

|

B28 |

GND |

|

|

Ground |

|

B29 |

AD21 |

|

|

Address/Data 21 |

|

B30 |

AD19 |

|

|

Address/Data 19 |

|

B31 |

+3.3V |

|

|

+3.3 VDC |

|

B32 |

AD17 |

|

|

Address/Data 17 |

|

B33 |

C/BE2 |

|

|

Command, Byte Enable 2 |

|

B34 |

GND13 |

|

|

Ground |

|

B35 |

IRDY |

|

|

Initiator Ready |

|

B36 |

+3.3V06 |

|

|

+3.3 VDC |

|

B37 |

DEVSEL |

|

|

Device Select |

|

B38 |

GND16 |

|

|

Ground |

|

B39 |

LOCK |

|

|

Lock bus |

|

B40 |

PERR |

|

|

Parity Error |

|

B41 |

+3.3V08 |

|

|

+3.3 VDC |

|

B42 |

SERR |

|

|

System Error |

|

B43 |

+3.3V09 |

|

|

+3.3 VDC |

|

B44 |

C/BE1 |

|

|

Command, Byte Enable 1 |

|

B45 |

AD14 |

|

|

Address/Data 14 |

|

B46 |

GND18 |

|

|

Ground |

|

B47 |

AD12 |

|

|

Address/Data 12 |

|

B48 |

AD10 |

|

|

Address/Data 10 |

|

B49 |

GND20 |

|

|

Ground |

|

B50 |

(OPEN) |

GND |

(OPEN) |

Ground or Open (Key) |

|

B51 |

(OPEN) |

GND |

(OPEN) |

Ground or Open (Key) |

|

B52 |

AD8 |

|

|

Address/Data 8 |

|

B53 |

AD7 |

|

|

Address/Data 7 |

|

B54 |

+3.3V12 |

|

|

+3.3 VDC |

|

B55 |

AD5 |

|

|

Address/Data 5 |

|

B56 |

AD3 |

|

|

Address/Data 3 |

|

B57 |

GND22 |

|

|

Ground |

|

B58 |

AD1 |

|

|

Address/Data 1 |

|

B59 |

VCC08 |

|

|

+5 VDC |

|

B60 |

ACK64 |

|

|

Acknowledge 64 bit ??? |

|

B61 |

VCC10 |

|

|

+5 VDC |

|

B62 |

VCC12 |

|

|

+5 VDC |

|

|

|

|

|

|

|

B63 |

RES |

|

|

Reserved |

|

B64 |

GND |

|

|

Ground |

|

B65 |

C/BE[6]# |

|

|

Command, Byte Enable 6 |

|

B66 |

C/BE[4]# |

|

|

Command, Byte Enable 4 |

|

B67 |

GND |

|

|

Ground |

|

B68 |

AD63 |

|

|

Address/Data 63 |

|

B69 |

AD61 |

|

|

Address/Data 61 |

|

B70 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

B71 |

AD59 |

|

|

Address/Data 59 |

|

B72 |

AD57 |

|

|

Address/Data 57 |

|

B73 |

GND |

|

|

Ground |

|

B74 |

AD55 |

|

|

Address/Data 55 |

|

B75 |

AD53 |

|

|

Address/Data 53 |

|

B76 |

GND |

|

|

Ground |

|

B77 |

AD51 |

|

|

Address/Data 51 |

|

B78 |

AD49 |

|

|

Address/Data 49 |

|

B79 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

B80 |

AD47 |

|

|

Address/Data 47 |

|

B81 |

AD45 |

|

|

Address/Data 45 |

|

B82 |

GND |

|

|

Ground |

|

B83 |

AD43 |

|

|

Address/Data 43 |

|

B84 |

AD41 |

|

|

Address/Data 41 |

|

B85 |

GND |

|

|

Ground |

|

B86 |

AD39 |

|

|

Address/Data 39 |

|

B87 |

AD37 |

|

|

Address/Data 37 |

|

B88 |

+5V |

+3.3V |

Signal Rail |

+V I/O (+5 V or +3.3 V) |

|

B89 |

AD35 |

|

|

Address/Data 35 |

|

B90 |

AD33 |

|

|

Address/Data 33 |

|

B91 |

GND |

|

|

Ground |

|

B92 |

RES |

|

|

Reserved |

|

B93 |

RES |

|

|

Reserved |

|

B94 |

GND |

|

|

Ground |

Diagrama de tempo:

Será mostrado o comportamento dos

sinais desse dispositivo:

___ ___ ___ ___ ___ ___

CLK ___| |___| |___| |___| |___| |___| |___

_______ _________

FRAME |_________________________________|

______ _______ ______ ______ ______

AD -------<______><_______><______><______><______>---

Address Data1 Data2 Data3 Data4

______ _______________________________

C/BE -------<______><_______________________________>---

Command Byte Enable Signals

____________ ___

IRDY |_________________________________|

_____________ ___

TRDY |________________________________|

______________ ___

DEVSEL |_______________________________|

PCI transfer cycle, 4 data phases, no wait states. Data is transferred on the rising edge of CLK.

[1] [2] [3]

___ ___ ___ ___ ___ ___ ___ ___

CLK ___| |___| |___| |___| |___| |___| |___| |___| |__

_______ _________

FRAME |________________________________________________|

A B C

______ ______________ ______ _____________

AD -------<______>---------<______________><______><_____________>---

Address Data1 Data2 Data3

______ ______________________________________________

C/BE -------<______><______________________________________________>---

Command Byte Enable Signals

Wait

____________ _____ ___

IRDY |__________________________________| |_______|

Wait Wait

______________________ ______ ___

TRDY |_______| |_______________________|

______________ ___

DEVSEL |______________________________________________|

PCI transfer cycle, with wait states. Data in